# Digital Design with CPLD Applications and VHDL

Dueck

## Basic Principles of Digital **Systems**

#### OUTLINE

- **1.1** Digital Versus **Analog Electronics**

- 1.2 Digital Logic Levels

- 1.3 The Binary Number System

- **1.4** Hexadecimal Numbers

- **1.5** Digital Waveforms

#### CHAPTER OBJECTIVES

Upon successful completion of this chapter, you will be able to:

- Describe some differences between analog and digital electronics.

- Understand the concept of HIGH and LOW logic levels.

- Explain the basic principles of a positional notation number system.

- Translate logic HIGHs and LOWs into binary numbers.

- Count in binary, decimal, or hexadecimal.

- Convert a number in binary, decimal, or hexadecimal to any of the other number bases.

- Calculate the fractional binary equivalent of any decimal number.

- Distinguish between the most significant bit and least significant bit of a bi-

- Describe the difference between periodic, aperiodic, and pulse waveforms.

- Calculate the frequency, period, and duty cycle of a periodic digital wave-

- Calculate the pulse width, rise time, and fall time of a digital pulse.

igital electronics is the branch of electronics based on the combination and switching of voltages called logic levels. Any quantity in the outside world, such as temperature, pressure, or voltage, can be symbolized in a digital circuit by a group of logic voltages that, taken together, represent a binary number.

Each logic level corresponds to a digit in the binary (base 2) number system. The binary digits, or bits, 0 and 1, are sufficient to write any number, given enough places. The hexadecimal (base 16) number system is also important in digital systems. Since every combination of four binary digits can be uniquely represented as a hexadecimal digit, this system is often used as a compact way of writing binary information.

Inputs and outputs in digital circuits are not always static. Often they vary with time. Time-varying digital waveforms can have three forms:

- 1. Periodic waveforms, which repeat a pattern of logic 1s and 0s

- 2. Aperiodic waveforms, which do not repeat

- 3. Pulse waveforms, which produce a momentary variation from a constant logic level

## **1.1** Digital Versus Analog Electronics

#### KEY TERMS

**Continuous** Smoothly connected. An unbroken series of consecutive values with no instantaneous changes.

**Discrete** Separated into distinct segments or pieces. A series of discontinuous values.

**Analog** A way of representing some physical quantity, such as temperature or velocity, by a proportional continuous voltage or current. An analog voltage or current can have any value within a defined range.

**Digital** A way of representing a physical quantity by a series of binary numbers. A digital representation can have only specific discrete values.

The study of electronics often is divided into two basic areas: **analog** and **digital** electronics. Analog electronics has a longer history and can be regarded as the "classical" branch of electronics. Digital electronics, although newer, has achieved greater prominence through the advent of the computer age. The modern revolution in microcomputer chips, as part of everything from personal computers to cars and coffee makers, is founded almost entirely on digital electronics.

The main difference between analog and digital electronics can be stated simply. Analog voltages or currents are **continuously** variable between defined values, and digital voltages or currents can vary only by distinct, or **discrete**, steps.

Some keywords highlight the differences between digital and analog electronics:

| Analog                | Digital       |

|-----------------------|---------------|

| Continuously variable | Discrete step |

| Amplification         | Switching     |

| Voltages              | Numbers       |

An example often used to illustrate the difference between analog and digital devices is the comparison between a light dimmer and a light switch. A light dimmer is an analog device, since it can make the light it controls vary in brightness anywhere within a defined range of values. The light can be fully on, fully off, or at some brightness level in between. A light switch is a digital device, since it can turn the light on or off, but there is no value in between those two states.

The light switch/light dimmer analogy, although easy to understand, does not show any particular advantage to the digital device. If anything, it makes the digital device seem limited.

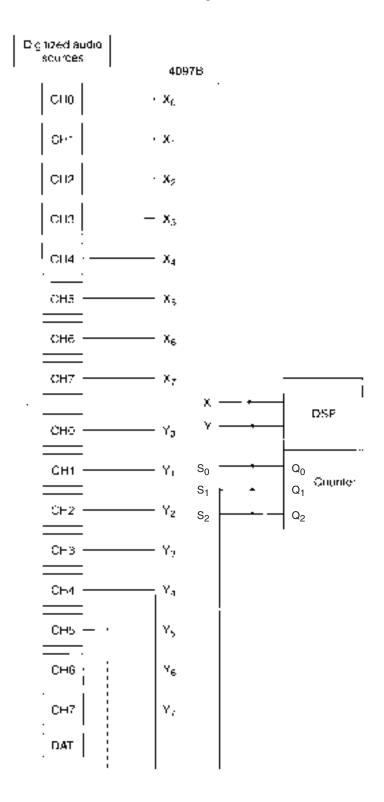

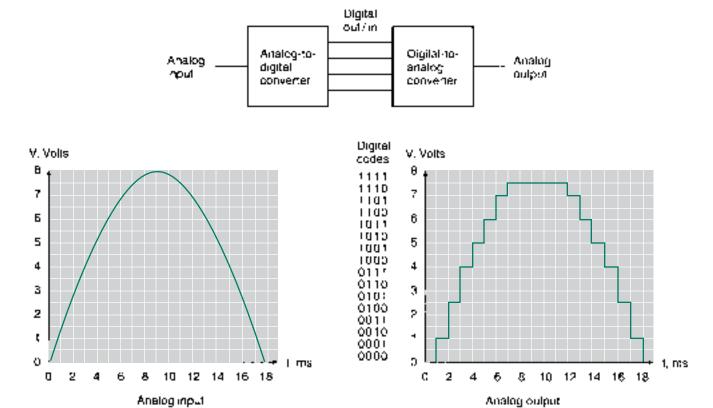

One modern application in which a digital device is clearly superior to an analog one is digital audio reproduction. Compact disc players have achieved their high level of popularity because of the accurate and noise-free way in which they reproduce recorded music. This high quality of sound is possible because the music is stored, not as a magnetic copy of the sound vibrations, as in analog tapes, but as a series of numbers that represent amplitude steps in the sound waves.

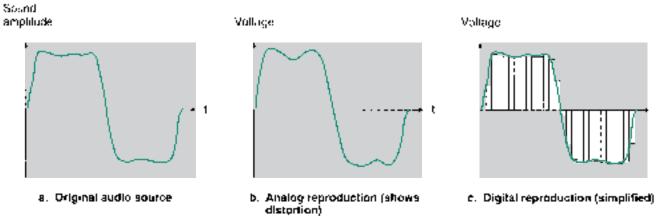

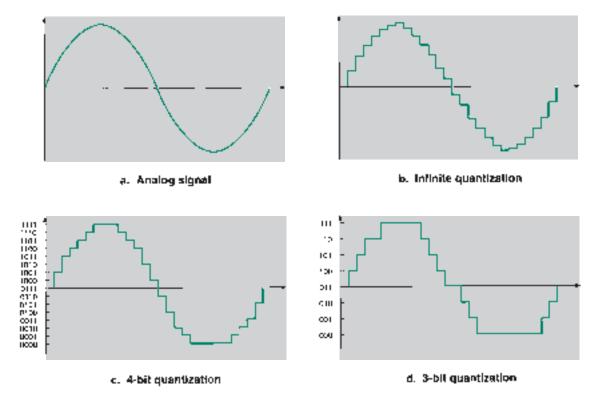

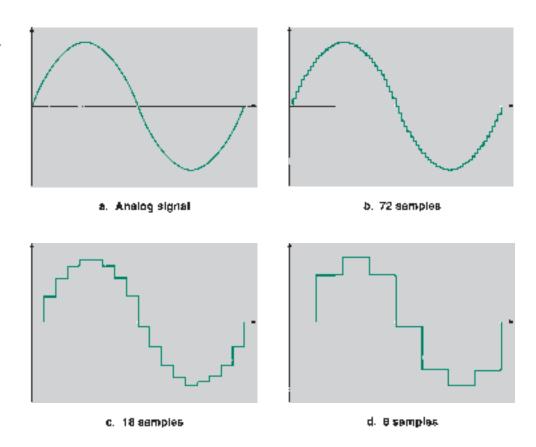

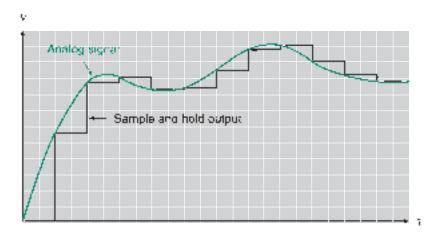

Figure 1.1 shows a sound waveform and its representation in both analog and digital forms.

The analog voltage, shown in Figure 1.1b, is a copy of the original waveform and introduces distortion both in the storage and playback processes. (Think of how a photocopy deteriorates in quality if you make a copy of a copy, then a copy of the new copy, and so on. It doesn't take long before you can't read the fine print.)

A digital audio system doesn't make a copy of the waveform, but rather stores a code (a series of amplitude numbers) that tells the compact disc player how to re-create the original sound every time a disc is played. During the recording process, the sound waveform

**FIGURE 1.1** Digital and Analog Sound Reproduction

is "sampled" at precise intervals. The recording transforms each sample into a digital number corresponding to the amplitude of the sound at that point.

The "samples" (the voltages represented by the vertical bars) of the digitized audio waveform shown in Figure 1.1c are much more widely spaced than they would be in a real digital audio system. They are shown this way to give the general idea of a digitized waveform. In real digital audio systems, each amplitude value can be indicated by a number having as many as 16,000 to 65,000 possible values. Such a large number of possible values means the voltage difference between any two consecutive digital numbers is very small. The numbers can thus correspond extremely closely to the actual amplitude of the sound waveform. If the spacing between the samples is made small enough, the reproduced waveform is almost exactly the same as the original.

#### **III** SECTION 1.1 REVIEW PROBLEM

1.1 What is the basic difference between analog and digital audio reproduction?

## 1.2 Digital Logic Levels

#### KEY TERMS

**Logic level** A voltage level that represents a defined digital state in an electronic circuit.

**Logic HIGH** (or **logic 1**) The higher of two voltages in a digital system with two logic levels.

**Logic LOW** (or **logic 0**) The lower of two voltages in a digital system with two logic levels.

**Positive logic** A system in which logic LOW represents binary digit 0 and logic HIGH represents binary digit 1.

**Negative logic** A system in which logic LOW represents binary digit 1 and logic HIGH represents binary digit 0.

Digitally represented quantities, such as the amplitude of an audio waveform, are usually represented by binary, or base 2, numbers. When we want to describe a digital quantity electronically, we need to have a system that uses voltages or currents to symbolize binary numbers.

The binary number system has only two digits, 0 and 1. Each of these digits can be denoted by a different voltage called a **logic level**. For a system having two logic levels, the

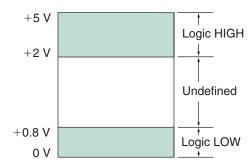

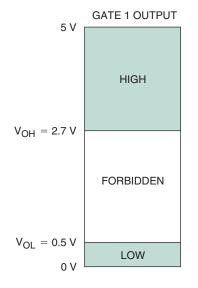

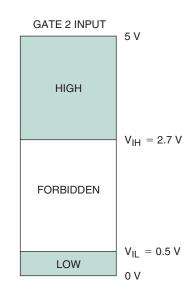

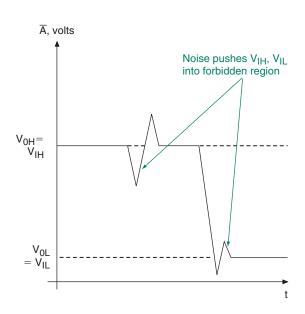

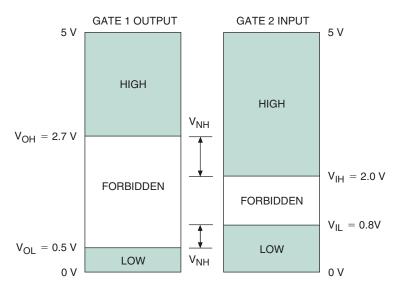

lower voltage (usually 0 volts) is called a **logic LOW** or **logic 0** and represents the digit 0. The higher voltage (traditionally 5 V, but in some systems a specific value such as 1.8 V, 2.5 V or 3.3 V) is called a **logic HIGH** or **logic 1**, which symbolizes the digit 1. Except for some allowable tolerance, as shown in Figure 1.2, the range of voltages between HIGH and LOW logic levels is undefined.

FIGURE 1.2 Logic Levels Based on +5 V and 0 V

#### NOTE

For the voltages in Figure 1.2:

$$+5 \text{ V} = \text{Logic HIGH} = 1$$

$0 \text{ V} = \text{Logic LOW} = 0$

The system assigning the digit 1 to a logic HIGH and digit 0 to logic LOW is called **positive logic.** Throughout the remainder of this text, logic levels will be referred to as HIGH/LOW or 1/0 interchangeably.

(A complementary system, called **negative logic,** also exists that makes the assignment the other way around.)

## 1.3 The Binary Number System

#### KEY TERMS

**Binary number system** A number system used extensively in digital systems, based on the number 2. It uses two digits, 0 and 1, to write any number.

**Positional notation** A system of writing numbers where the value of a digit depends not only on the digit, but also on its placement within a number.

**Bit** Binary digit. A 0 or a 1.

#### **Positional Notation**

The **binary number system** is based on the number 2. This means that we can write any number using only two binary digits (or **bits**), 0 and 1. Compare this to the decimal system, which is based on the number 10, where we can write any number with only ten decimal digits, 0 to 9.

The binary and decimal systems are both **positional notation** systems; the value of a digit in either system depends on its placement within a number. In the decimal number 845, the digit 4 really means 40, whereas in the number 9426, the digit 4 really means 400 (845 = 800 + 40 + 5; 9426 = 9000 + 400 + 20 + 6). The value of the digit is determined by *what* the digit is as well as *where* it is.

In the decimal system, a digit in the position immediately to the left of the decimal point is multiplied by  $1 (10^0)$ . A digit two positions to the left of the decimal point is mul-

tiplied by  $10 (10^1)$ . A digit in the next position left is multiplied by  $100 (10^2)$ . The positional multipliers, as you move left from the decimal point, are ascending powers of 10.

The same idea applies in the binary system, except that the positional multipliers are powers of 2 ( $2^0 = 1$ ,  $2^1 = 2$ ,  $2^2 = 4$ ,  $2^3 = 8$ ,  $2^4 = 16$ ,  $2^5 = 32$ , . .). For example, the binary number 101 has the decimal equivalent:

$$(1 \times 2^{2}) + (0 \times 2^{1}) + (1 \times 2^{0})$$

$$= (1 \times 4) + (0 \times 2) + (1 \times 1)$$

$$= 4 + 0 + 1$$

$$= 5$$

#### **III** EXAMPLE 1.1

Calculate the decimal equivalents of the binary numbers 1010, 111, and 10010.

SOLUTIONS

$$1010 = (1 \times 2^{3}) + (0 \times 2^{2}) + (1 \times 2^{1}) + (0 \times 2^{0})$$

$$= (1 \times 8) + (0 \times 4) + (1 \times 2) + (0 \times 1)$$

$$= 8 + 2 = 10$$

$$111 = (1 \times 2^{2}) + (1 \times 2^{1}) + (1 \times 2^{0})$$

$$= (1 \times 4) + (1 \times 2) + (1 \times 1)$$

$$= 4 + 2 + 1 = 7$$

$$10010 = (1 \times 2^{4}) + (0 \times 2^{3}) + (0 \times 2^{2}) + (1 \times 2^{1}) + (0 \times 2^{0})$$

$$= (1 \times 16) + (0 \times 8) + (0 \times 4) + (1 \times 2) + (0 \times 1)$$

$$= 16 + 2 = 18$$

### **Binary Inputs**

#### KEY TERMS

**Most significant bit** The leftmost bit in a binary number. This bit has the number's largest positional multiplier.

**Least significant bit** The rightmost bit of a binary number. This bit has the number's smallest positional multiplier.

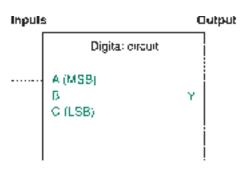

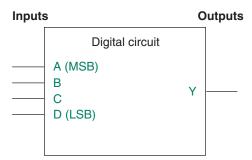

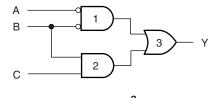

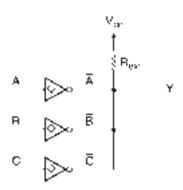

A major class of digital circuits, called combinational logic, operates by accepting logic levels at one or more input terminals and producing a logic level at an output. In the analysis and design of such circuits, it is frequently necessary to find the output logic level of a circuit for all possible combinations of input logic levels.

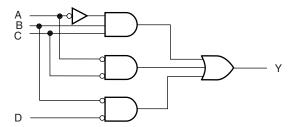

The digital circuit in the black box in Figure 1.3 has three inputs. Each input can have two possible states, LOW or HIGH, which can be represented by positive logic as 0 or 1. The number of possible input combinations is  $2^3 = 8$ . (In general, a circuit with n binary inputs has  $2^n$  input combinations, ranging from 0 to  $2^n - 1$ .) Table 1.1 shows a list of these combinations, both as logic levels and binary numbers, and their decimal equivalents.

**FIGURE 1.3**3-Input Digital Circuit

6

**TABLE 1.1** Possible Input Combinations for a 3-Input Digital Circuit

A list of output logic levels corresponding to all possible input combinations, applied in ascending binary order, is called a truth table. This is a standard form for showing the function of a digital circuit.

The input bits on each line of Table 1.1 can be read from left to right as a series of 3-bit binary numbers. The numerical values of these eight input combinations range from 0 to 7 ( $2^n$  possible input combinations, having decimal equivalents ranging from 0 to  $2^n-1$ ) in decimal.

Bit *A* is called the **most significant bit** (MSB), and bit *C* is called the **least significant bit** (LSB). As these terms imply, a change in bit *A* is more significant, since it has the greatest effect on the number of which it is part.

Table 1.2 shows the effect of changing each of these bits in a 3-bit binary number and compares the changed number to the original by showing the difference in magnitude. A change in the MSB of any 3-bit number results in a difference of 4. A change in the LSB of any binary number results in a difference of 1. (Try it with a few different numbers.)

**TABLE 1.2** Effect of Changing the LSB and MSB of a Binary Number

|            | $\boldsymbol{A}$ | В | C | Decimal |                  |

|------------|------------------|---|---|---------|------------------|

| Original   | 0                | 1 | 1 | 3       |                  |

| Change MSB | 1                | 1 | 1 | 7       | Difference $= 4$ |

| Change LSB | 0                | 1 | 0 | 2       | Difference = 1   |

#### **III** EXAMPLE 1.2

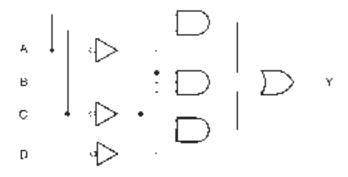

Figure 1.4 shows a 4-input digital circuit. List all the possible binary input combinations to this circuit and their decimal equivalents. What is the value of the MSB?

FIGURE 1.4

Example 1.2: 4-Input Digital Circuit

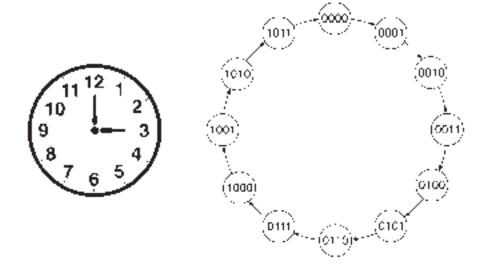

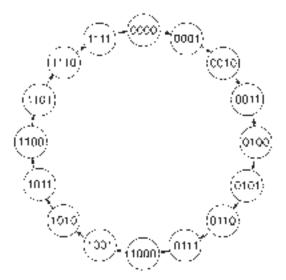

**SOLUTION** Since there are four inputs, there will be  $2^4 = 16$  possible input combinations, ranging from 0000 to 1111 (0 to 15 in decimal). Table 1.3 shows the list of all possible input combinations.

The MSB has a value of 8 (decimal).

**TABLE 1.3** Possible Input Combinations for a 4-Input Digital Circuit

| A | В | C | D | Decimal |

|---|---|---|---|---------|

| 0 | 0 | 0 | 0 | 0       |

| 0 | 0 | 0 | 1 | 1       |

| 0 | 0 | 1 | 0 | 2       |

| 0 | 0 | 1 | 1 | 3       |

| 0 | 1 | 0 | 0 | 4       |

| 0 | 1 | 0 | 1 | 5       |

| 0 | 1 | 1 | 0 | 6       |

| 0 | 1 | 1 | 1 | 7       |

| 1 | 0 | 0 | 0 | 8       |

| 1 | 0 | 0 | 1 | 9       |

| 1 | 0 | 1 | 0 | 10      |

| 1 | 0 | 1 | 1 | 11      |

| 1 | 1 | 0 | 0 | 12      |

| 1 | 1 | 0 | 1 | 13      |

| 1 | 1 | 1 | 0 | 14      |

| 1 | 1 | 1 | 1 | 15      |

Knowing how to construct a binary sequence is a very important skill when working with digital logic systems. Two ways to do this are:

1. Learn to count in binary. You should know all the binary numbers from 0000 to 1111 and their decimal equivalents (0 to 15). Make this your first goal in learning the basics of digital systems.

Each binary number is a unique representation of its decimal equivalent. You can work out the decimal value of a binary number by adding the weighted values of all the bits.

For instance, the binary equivalent of the decimal sequence 0, 1, 2, 3 can be written using two bits: the 1's bit and the 2's bit. The binary count sequence is:

$$00 (= 0 + 0)$$

$$01 (= 0 + 1)$$

$$10 (= 2 + 0)$$

$$11 (= 2 + 1)$$

To count beyond this, you need another bit: the 4's bit. The decimal sequence 4, 5, 6, 7 has the binary equivalents:

$$100 (= 4 + 0 + 0)$$

$$101 (= 4 + 0 + 1)$$

$$110 (= 4 + 2 + 0)$$

$$111 (= 4 + 2 + 1)$$

The two least significant bits of this sequence are the same as the bits in the 0 to 3 sequence; a repeating pattern has been generated.

Ш

The sequence from 8 to 15 requires yet another bit: the 8's bit. The three LSBs of this sequence repeat the 0 to 7 sequence. The binary equivalents of 8 to 15 are:

$$1000 (= 8 + 0 + 0 + 0)$$

$$1001 (= 8 + 0 + 0 + 1)$$

$$1010 (= 8 + 0 + 2 + 0)$$

$$1011 (= 8 + 0 + 2 + 1)$$

$$1100 (= 8 + 4 + 0 + 0)$$

$$1101 (= 8 + 4 + 0 + 1)$$

$$1110 (= 8 + 4 + 2 + 0)$$

$$1111 (= 8 + 4 + 2 + 1)$$

Practice writing out the binary sequence until it becomes familiar. In the 0 to 15 sequence, it is standard practice to write each number as a 4-bit value, as in Example 1.2, so that all numbers have the same number of bits. Numbers up to 7 have leading zeros to pad them out to 4 bits.

This convention has developed because each bit has a physical location in a digital circuit; we know a particular bit is logic 0 because we can measure 0 V at a particular point in a circuit. A bit with a value of 0 doesn't go away just because there is not a 1 at a more significant location.

While you are still learning to count in binary, you can use a second method.

2. Follow a simple repetitive pattern. Look at Tables 1.1 and 1.3 again. Notice that the least significant bit follows a pattern. The bits alternate with every line, producing the pattern 0, 1, 0, 1, . . . . The 2's bit alternates every two lines: 0, 0, 1, 1, 0, 0, 1, 1, . . . . The 4's bit alternates every four lines: 0, 0, 0, 0, 1, 1, 1, 1, . . . . This pattern can be expanded to cover any number of bits, with the number of lines between alternations doubling with each bit to the left.

#### **Decimal-to-Binary Conversion**

There are two methods commonly used to convert decimal numbers to binary: sum of powers of 2 and repeated division by 2.

#### Sum of Powers of 2

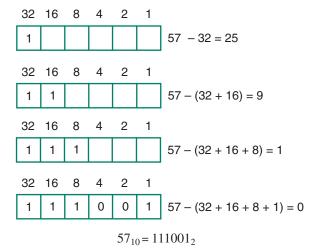

You can convert a decimal number to binary by adding up powers of 2 by inspection, adding bits as you need them to fill up the total value of the number. For example, convert  $57_{10}$  to binary.

$$64_{10} > 57_{10} > 32_{10}$$

• We see that  $32 (=2^5)$  is the largest power of two that is smaller than 57. Set the 32's bit to 1 and subtract 32 from the original number, as shown below.

$$57 - 32 = 25$$

• The largest power of two that is less than 25 is 16. Set the 16's bit to 1 and subtract 16 from the accumulated total.

$$25 - 16 = 9$$

• 8 is the largest power of two that is less than 9. Set the 8's bit to 1 and subtract 8 from the total.

$$9 - 8 = 1$$

- 4 is greater than the remaining total. Set the 4's bit to 0.

- 2 is greater than the remaining total. Set the 2's bit to 0.

• 1 is left over. Set the 1's bit to 1 and subtract 1.

$$1 - 1 = 0$$

• Conversion is complete when there is nothing left to subtract. Any remaining bits should be set to 0.

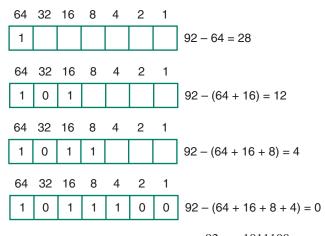

Convert 92<sub>10</sub> to binary using the sum-of-powers-of-2 method.

#### **SOLUTION**

**III** EXAMPLE 1.3

$92_{10} = 1011100_2$

#### Repeated Division by 2

Any decimal number divided by 2 will leave a remainder of 0 or 1. Repeated division by 2 will leave a string of 0s and 1s that become the binary equivalent of the decimal number. Let us use this method to convert  $46_{10}$  to binary.

1. Divide the decimal number by 2 and note the remainder.

$$46/2 = 23 + \text{remainder } 0 \text{ (LSB)}$$

The remainder is the least significant bit of the binary equivalent of 46.

Divide the quotient from the previous division and note the remainder. The remainder is the second LSB.

$$23/2 = 11 + \text{remainder } 1$$

$$11/2 = 5 + \text{remainder } 1$$

$5/2 = 2 + \text{remainder } 1$

$2/2 = 1 + \text{remainder } 0$

$1/2 = 0 + \text{remainder } 1$  (MSB)

To write the binary equivalent of the decimal number, read the remainders from the bottom up.

$$46_{10} = 101110_2$$

#### **III** EXAMPLE 1.4

Use repeated division by 2 to convert  $115_{10}$  to a binary number.

**SOLUTION**

$$115/2 = 57 + \text{remainder 1 (LSB)}$$

57/2 = 28 + remainder 1 28/2 = 14 + remainder 0 14/2 = 7 + remainder 0 7/2 = 3 + remainder 1 3/2 = 1 + remainder 1 1/2 = 0 + remainder 1 (MSB)

Read the remainders from bottom to top: 1110011.

$$115_{10} = 1110011_2$$

In any decimal-to-binary conversion, the number of bits in the binary number is the exponent of the smallest power of 2 that is larger than the decimal number.

For example, for the numbers  $92_{10}$  and  $46_{10}$ ,

$$2^7 = 128 > 92$$

7 bits: 1011100

$2^6 = 64 > 46$  6 bits: 101110

## **Fractional Binary Numbers**

#### KEY TERMS

**Radix point** The generalized form of a decimal point. In any positional number system, the radix point marks the dividing line between positional multipliers that are positive and negative powers of the system's number base.

**Binary point** A period (".") that marks the dividing line between positional multipliers that are positive and negative powers of 2 (e.g., first multiplier right of binary point =  $2^{-1}$ ; first multiplier left of binary point =  $2^{0}$ ).

In the decimal system, fractional numbers use the same digits as whole numbers, but the digits are written to the right of the decimal point. The multipliers for these digits are negative powers of  $10-10^{-1}$  (1/10),  $10^{-2}$  (1/100),  $10^{-3}$  (1/1000), and so on.

So it is in the binary system. Digits 0 and 1 are used to write fractional binary numbers, but the digits are to the right of the **binary point**—the binary equivalent of the decimal point. (The decimal point and binary point are special cases of the **radix point**, the general name for any such point in any number system.)

Ш

Each digit is multiplied by a positional factor that is a negative power of 2. The first four multipliers on either side of the binary point are:

binary point

$$2^{3} 2^{2} 2^{1} 2^{0} \cdot 2^{-1} 2^{-2} 2^{-3} 2^{-4}$$

$$= 8 = 4 = 2 = 1 = 1/2 = 1/4 = 1/8 = 1/16$$

#### **III** EXAMPLE 1.5

Write the binary fraction 0.101101 as a decimal fraction.

SOLUTION

$$1 \times 1/2 = 1/2$$

$$0 \times 1/4 = 0$$

$$1 \times 1/8 = 1/8$$

$$1 \times 1/16 = 1/16$$

$$0 \times 1/32 = 0$$

$$1 \times 1/64 = 1/64$$

$$1/2 + 1/8 + 1/16 + 1/64 = 32/64 + 8/64 + 4/64 + 1/64$$

$$= 45/64$$

$$= 0.703125_{10}$$

#### Fractional-Decimal-to-Fractional-Binary Conversion

Simple decimal fractions such as 0.5, 0.25, and 0.375 can be converted to binary fractions by a sum-of-powers method. The above decimal numbers can also be written 0.5 = 1/2, 0.25 = 1/4, and 0.375 = 3/8 = 1/4 + 1/8. These numbers can all be represented by negative powers of 2. Thus, in binary,

$$0.5_{10} = 0.1_2$$

$0.25_{10} = 0.01_2$

$0.375_{10} = 0.011_2$

The conversion process becomes more complicated if we try to convert decimal fractions that cannot be broken into powers of 2. For example, the number  $1/5 = 0.2_{10}$  cannot be exactly represented by a sum of negative powers of 2. (Try it.) For this type of number, we must use the method of repeated multiplication by 2.

#### Method:

1. Multiply the decimal fraction by 2 and note the integer part. The integer part is either 0 or 1 for any number between 0 and 0.999. . . . The integer part of the product is the first digit to the left of the binary point.

$$0.2 \times 2 = 0.4$$

Integer part: 0

2. Discard the integer part of the previous product. Multiply the fractional part of the previous product by 2. Repeat step 1 until the fraction repeats or terminates.

$$0.4 \times 2 = 0.8$$

Integer part: 0

$0.8 \times 2 = 1.6$  Integer part: 1

$0.6 \times 2 = 1.2$  Integer part: 1

$0.2 \times 2 = 0.4$  Integer part: 0

(Fraction repeats; product is same as in step 1)

Read the above integer parts from top to bottom to obtain the fractional binary number. Thus,  $0.2_{10} = 0.00110011$ . . .  $._2 = 0.\overline{0011}_2$ . The bar shows the portion of the digits that repeats.

#### **EXAMPLE 1.6**

Convert 0.95<sub>10</sub> to its binary equivalent.

| SOLUTION | $0.95 \times 2 = 1.90$ | Integer part: 1                   |

|----------|------------------------|-----------------------------------|

|          | $0.90 \times 2 = 1.80$ | Integer part: 1                   |

|          | $0.80 \times 2 = 1.60$ | Integer part: 1                   |

|          | $0.60 \times 2 = 1.20$ | Integer part: 1                   |

|          | $0.20 \times 2 = 0.40$ | Integer part: 0                   |

|          | $0.40 \times 2 = 0.80$ | Integer part: 0                   |

|          | $0.80 \times 2 = 1.60$ | Fraction repeats last four digits |

|          | 0.9                    | $95_{10} = 0.11\overline{1100}_2$ |

#### **■ SECTION 1.3 REVIEW PROBLEMS**

- 1.2. How many different binary numbers can be written with 6 bits?

- 1.3. How many can be written with 7 bits?

- 1.4. Write the sequence of 7-bit numbers from 1010000 to 1010111.

- 1.5. Write the decimal equivalents of the numbers written for Problem 1.4.

#### **1.4** Hexadecimal Numbers

After binary numbers, hexadecimal (base 16) numbers are the most important numbers in digital applications. Hexadecimal, or hex, numbers are primarily used as a shorthand form of binary notation. Since 16 is a power of 2 ( $2^4 = 16$ ), each hexadecimal digit can be converted directly to four binary digits. Hex numbers can pack more digital information into fewer digits.

Hex numbers have become particularly popular with the advent of small computers, which use binary data having 8, 16, or 32 bits. Such data can be represented by 2, 4, or 8 hexadecimal digits, respectively.

**TABLE 1.4** Hex Digits and Their Binary and Decimal Equivalents

| Hex | Decimal | Binary |

|-----|---------|--------|

| 0   | 0       | 0000   |

| 1   | 1       | 0001   |

| 2   | 2       | 0010   |

| 3   | 3       | 0011   |

| 4   | 4       | 0100   |

| 5   | 5       | 0101   |

| 6   | 6       | 0110   |

| 7   | 7       | 0111   |

| 8   | 8       | 1000   |

| 9   | 9       | 1001   |

| A   | 10      | 1010   |

| В   | 11      | 1011   |

| C   | 12      | 1100   |

| D   | 13      | 1101   |

| E   | 14      | 1110   |

| F   | 15      | 1111   |

|     |         |        |

#### Counting in Hexadecimal

The positional multipliers in the hex system are powers of sixteen:  $16^0 = 1$ ,  $16^1 = 16$ ,  $16^2 = 256$ ,  $16^3 = 4096$ , and so on.

We need 16 digits to write hex numbers; the decimal digits 0 through 9 are not sufficient. The usual convention is to use the capital letters A through F, each letter representing a number from  $10_{10}$  through  $15_{10}$ . Table 1.4 shows how hexadecimal digits relate to their decimal and binary equivalents.

#### NOTE

#### **Counting Rules for Hexadecimal Numbers:**

- 1. Count in sequence from 0 to F in the least significant digit.

- 2. Add 1 to the next digit to the left and start over.

- 3. Repeat in all other columns.

For instance, the hex numbers between 19 and 22 are 19, 1A, 1B, 1C, 1D, 1E, 1F, 20, 21, 22. (The decimal equivalents of these numbers are  $25_{10}$  through  $34_{10}$ .)

13

П

What is the next hexadecimal number after 999? After 99F? After 9FF? After FFF?

**SOLUTION** The hexadecimal number after 999 is 99A. The number after 99F is 9A0. The number after 9FF is A00. The number after FFF is 1000.

#### **EXAMPLE 1.8**

List the hexadecimal digits from  $190_{16}$  to  $200_{16}$ , inclusive.

**SOLUTION** The numbers follow the counting rules: Use all the digits in one position, add 1 to the digit one position left, and start over.

For brevity, we will list only a few of the numbers in the sequence:

#### **III** SECTION 1.4A REVIEW PROBLEMS

- 1.6. List the hexadecimal numbers from FA9 to FB0, inclusive.

- 1.7. List the hexadecimal numbers from 1F9 to 200, inclusive.

#### Hexadecimal-to-Decimal Conversion

To convert a number from hex to decimal, multiply each digit by its power-of-16 positional multiplier and add the products. In the following examples, hexadecimal numbers are indicated by a final "H" (e.g., 1F7H), rather than a "16" subscript.

#### **III** EXAMPLE 1.9

Convert 7C6H to decimal.

**SOLUTION**

$$7 \times 16^{2} = 7_{10} \times 256_{10} = 1792_{10}$$

$$C \times 16^{1} = 12_{10} \times 16_{10} = 192_{10}$$

$$6 \times 16^{0} = 6_{10} \times 1_{10} = 6_{10}$$

$$1990_{10}$$

#### **III** EXAMPLE 1.10

Convert 1FD5H to decimal.

**SOLUTION**

#### **■ SECTION 1.4B REVIEW PROBLEM**

1.8 Convert the hexadecimal number A30F to its decimal equivalent.

#### Decimal-to-Hexadecimal Conversion

Decimal numbers can be converted to hex by the sum-of-weighted-hex-digits method or by repeated division by 16. The main difficulty we encounter in either method is

remembering to convert decimal numbers 10 through 15 into the equivalent hex digits, A through F.

#### **Sum of Weighted Hexadecimal Digits**

This method is useful for simple conversions (about three digits). For example, the decimal number 35 is easily converted to the hex value 23.

$$35_{10} = 32_{10} + 3_{10} = (2 \times 16) + (3 \times 1) = 23H$$

#### **III** EXAMPLE 1.11

Convert 175<sub>10</sub> to hexadecimal.

#### **SOLUTION**

$$256_{10} > 175_{10} > 16_{10}$$

Since  $256 = 16^2$ , the hexadecimal number will have two digits.

$$(11 \times 16) > 175 > (10 \times 16)$$

$16 \quad 1$

$A \quad 175 - (A \times 16) = 175 - 160 = 15$

$16 \quad 1$

$A \quad F \quad 175 - ((A \times 16) + (F \times 1))$

$= 175 - (160 + 15) = 0$

П

#### Repeated Division by 16

Repeated division by 16 is a systematic decimal-to-hexadecimal conversion method that is not limited by the size of the number to be converted.

It is similar to the repeated-division-by-2 method used to convert decimal numbers to binary. Divide the decimal number by 16 and note the remainder, making sure to express it as a hex digit. Repeat the process until the quotient is zero. The last remainder is the most significant digit of the hex number.

#### **III** EXAMPLE 1.12

Convert 31581<sub>10</sub> to hexadecimal.

#### **SOLUTION**

#### **■ SECTION 1.4C REVIEW PROBLEM**

1.9 Convert the decimal number 8137 to its hexadecimal equivalent.

## Conversions Between Hexadecimal and Binary

Table 1.4 shows all 16 hexadecimal digits and their decimal and binary equivalents. Note that for every possible 4-bit binary number, there is a hexadecimal equivalent.

Binary-to-hex and hex-to-binary conversions simply consist of making a conversion between each hex digit and its binary equivalent.

#### **III** EXAMPLE 1.13

Convert 7EF8H to its binary equivalent.

**SOLUTION** Convert each digit individually to its equivalent value:

$7H = 0111_2$   $EH = 1110_2$   $FH = 1111_2$  $8H = 1000_2$

The binary number is all the above binary numbers in sequence:

$7EF8H = 11111110111111000_2$

The leading zero (the MSB of 0111) has been left out.

#### **III** SECTION 1.4D REVIEW PROBLEMS

- 1.10 Convert the hexadecimal number 934B to binary.

- 1.11 Convert the binary number 11001000001101001001 to hexadecimal.

## 1.5 Digital Waveforms

#### KEY TERM

**Digital waveform** A series of logic 1s and 0s plotted as a function of time.

The inputs and outputs of digital circuits often are not fixed logic levels but **digital waveforms**, where the input and output logic levels vary with time. There are three possible types of digital waveform. *Periodic* waveforms repeat the same pattern of logic levels over a specified period of time. *Aperiodic* waveforms do not repeat. *Pulse* waveforms follow a HIGH-LOW-HIGH or LOW-HIGH-LOW pattern and may be periodic or aperiodic.

#### **Periodic Waveforms**

#### KEY TERMS

**Periodic waveform** A time-varying sequence of logic HIGHs and LOWs that repeats over a specified period of time.

**Period** (*T*) Time required for a periodic waveform to repeat. Unit: seconds (*s*).

**Frequency** (f) Number of times per second that a periodic waveform repeats. f = 1/T Unit: Hertz (Hz).

**Time HIGH**  $(t_h)$  Time during one period that a waveform is in the HIGH state. Unit: seconds (s).

**Time LOW**  $(t_l)$  Time during one period that a waveform is in the LOW state. Unit: seconds (s).

**Duty cycle (***DC***)** Fraction of the total period that a digital waveform is in the HIGH state.  $DC = t_h/T$  (often expressed as a percentage:  $\%DC = t_h/T \times 100\%$ ).

**Periodic waveforms** repeat the same pattern of HIGHs and LOWs over a specified period of time. The waveform may or may not be symmetrical; that is, it may or may not be HIGH and LOW for equal amounts of time.

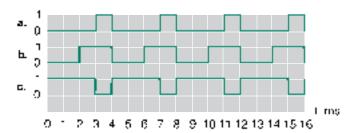

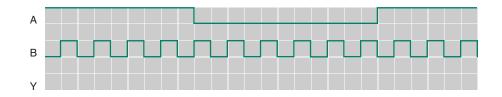

#### **III** EXAMPLE 1.14

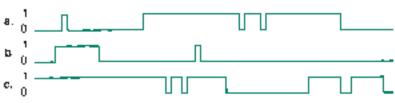

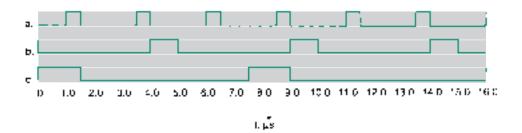

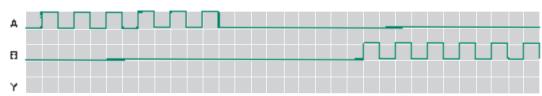

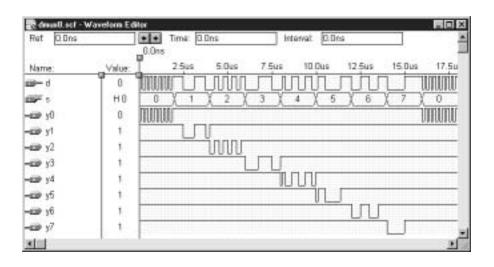

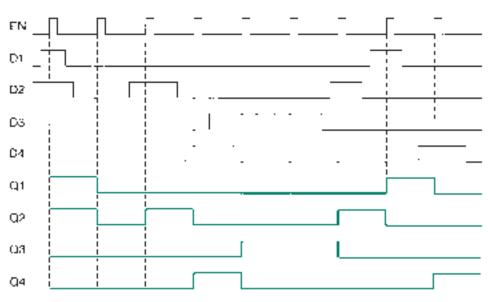

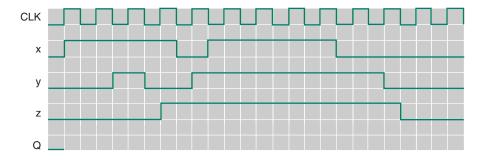

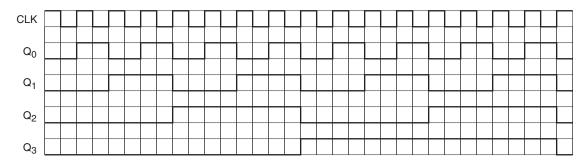

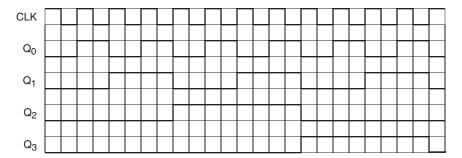

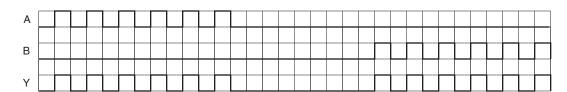

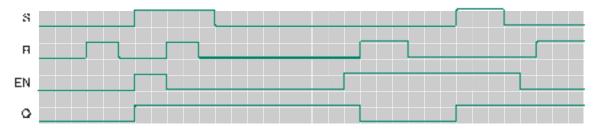

Calculate the **time LOW**, **time HIGH**, **period**, **frequency**, and **percent duty cycle** for each of the periodic waveforms in Figure 1.5.

#### FIGURE 1.5

Example 1.14: Periodic Digital Waveforms

How are the waveforms similar? How do they differ?

#### **SOLUTION**

a. Time LOW:  $t_l = 3 \text{ ms}$

Time HIGH:  $t_h = 1 \text{ ms}$

Period:  $T = t_l + t_h = 3 \text{ ms} + 1 \text{ ms} = 4 \text{ ms}$

Frequency: f = 1/T = 1/(4 ms) = 0.25 kHz = 250 Hz

Duty cycle:  $\%DC = (t_h/T) \times 100\% = (1 \text{ ms/4 ms}) \times 100\%$

= 25%

(1 ms = 1/1000 second; 1 kHz = 1000 Hz.)

b. Time LOW:  $t_l = 2 \text{ ms}$

Time HIGH:  $t_h = 2 \text{ ms}$

Period:  $T = t_l + t_h = 2 \text{ ms} + 2 \text{ ms} = 4 \text{ ms}$

Frequency: f = 1/T = 1/(4 ms) = 0.25 kHz = 250 Hz

Duty cycle:  $\%DC = (t_h/T) \times 100\% = (2 \text{ ms/ } 4 \text{ ms}) \times 100\%$

= 50%

c. Time LOW:  $t_l = 1 \text{ ms}$

Time HIGH:  $t_h = 3 \text{ ms}$

Period:  $T = t_1 + t_h = 1 \text{ ms} + 3 \text{ ms} = 4 \text{ ms}$

Frequency: f = 1/T = 1/(4 ms) = 0.25 kHz and 250 Hz

Duty cycle:  $\%DC = (t_h/T) \times 100\% = (3 \text{ ms/ } 4 \text{ ms}) \times 100\%$

= 75%

The waveforms all have the same period but different duty cycles. A square waveform, shown in Figure 1.5b, has a duty cycle of 50%.

## **Aperiodic Waveforms**

#### KEY TERM

**Aperiodic waveform** A time-varying sequence of logic HIGHs and LOWs that does not repeat.

An **aperiodic waveform** does not repeat a pattern of 0s and 1s. Thus, the parameters of time HIGH, time LOW, frequency, period, and duty cycle have no meaning for an aperiodic waveform. Most waveforms of this type are one-of-a-kind specimens. (It is also worth noting that most digital waveforms are aperiodic.)

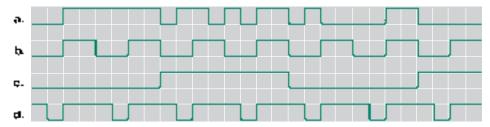

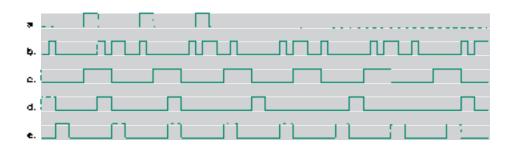

Figure 1.6 shows some examples of aperiodic waveforms.

#### FIGURE 1.6

Aperiodic Digital Waveforms

#### **III** EXAMPLE 1.15

A digital circuit generates the following strings of 0s and 1s:

- a. 00111111101101011010000110000

- b. 0011001100110011001100110011

- c. 000000001111111111000000001111

- d. 1011101110111011101110111011

The time between two bits is always the same. Sketch the resulting digital waveform for each string of bits. Which waveforms are periodic and which are aperiodic?

**SOLUTION** Figure 1.7 shows the waveforms corresponding to the strings of bits above. The waveforms are easier to draw if you break up the bit strings into smaller groups of, say, 4 bits each. For instance:

a. 0011 1111 0110 1011 0100 0011 0000

All of the waveforms except Figure 1.7a are periodic.

FIGURE 1.7

Example 1.15: Waveforms

#### **Pulse Waveforms**

#### KEY TERMS

**Pulse** A momentary variation of voltage from one logic level to the opposite level and back again.

**Amplitude** The instantaneous voltage of a waveform. Often used to mean maximum amplitude, or peak voltage, of a pulse.

**Edge** The part of the pulse that represents the transition from one logic level to the other.

**Rising edge** The part of a pulse where the logic level is in transition from a LOW to a HIGH.

**Falling edge** The part of a pulse where the logic level is a transition from a HIGH to a LOW.

**Leading edge** The edge of a pulse that occurs earliest in time.

**Trailing edge** The edge of a pulse that occurs latest in time.

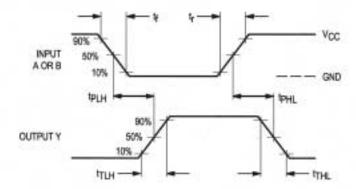

**Pulse width**  $(t_w)$  Elapsed time from the 50% point of the leading edge of a pulse to the 50% point of the trailing edge.

**Rise time**  $(t_r)$  Elapsed time from the 10% point to the 90% point of the rising edge of a pulse.

**Fall time**  $(t_f)$  Elapsed time from the 90% point to the 10% point of the falling edge of a pulse.

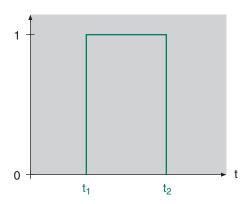

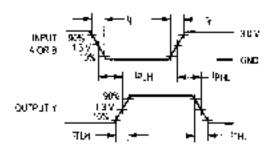

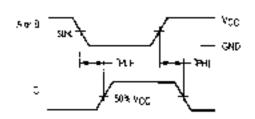

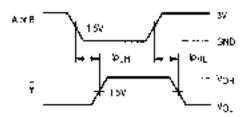

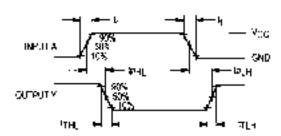

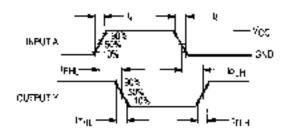

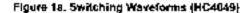

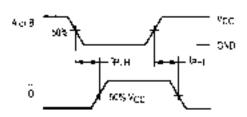

Figure 1.8 shows the forms of both an ideal and a nonideal **pulse.** The **rising and falling edges** of an ideal pulse are vertical. That is, the transitions between logic HIGH and LOW levels are instantaneous. There is no such thing as an ideal pulse in a real digital circuit. Circuit capacitance and other factors make the pulse more like the nonideal pulse in Figure 1.8b.

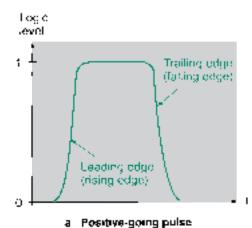

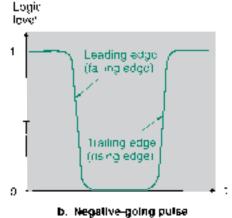

Pulses can be either positive-going or negative-going, as shown in Figure 1.9. In a positive-going pulse, the measured logic level is normally LOW, goes HIGH for the duration

a. Ideal pulse (instantaneous transitions) FIGURE 1.8

Ideal and Nonideal Pulses

b. Nonideal pulse

FIGURE 1.9

Pulse Edges

of the pulse, and returns to the LOW state. A negative-going pulse acts in the opposite direction.

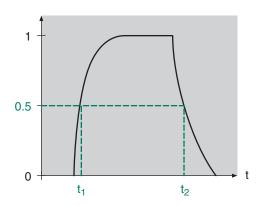

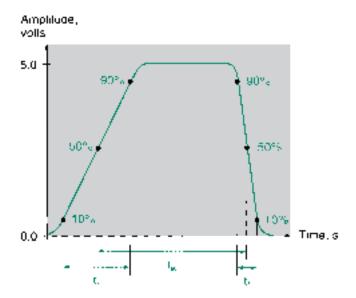

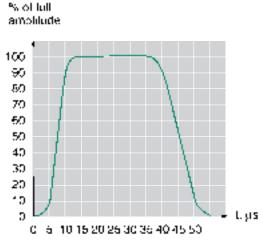

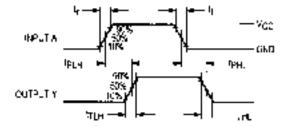

Nonideal pulses are measured in terms of several timing parameters. Figure 1.10 shows the 10%, 50%, and 90% points on the rising and falling edges of a nonideal pulse. (100% is the maximum **amplitude** of the pulse.)

FIGURE 1.10 Pulse Width, Rise Time, Fall Time

The 50% points are used to measure **pulse width** because the edges of the pulse are not vertical. Without an agreed reference point, the pulse width is indeterminate. The 10% and 90% points are used as references for the **rise and fall times**, since the edges of a nonideal pulse are nonlinear. Most of the nonlinearity is below the 10% or above the 90% point.

#### **III** EXAMPLE 1.16

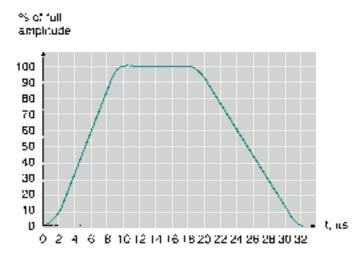

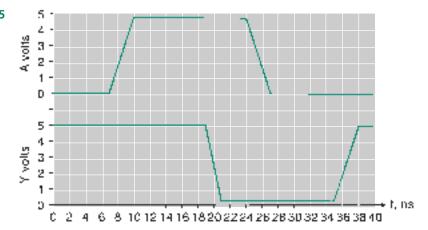

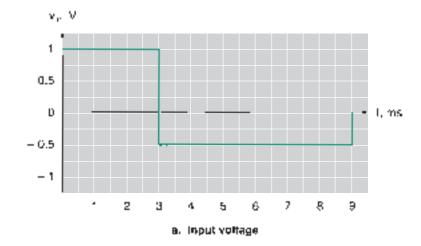

Calculate the pulse width, rise time, and fall time of the pulse shown in Figure 1.11.

#### FIGURE 1.11 Example 1.16: Pulse

**SOLUTION** From the graph in Figure 1.11, read the times corresponding to the 10%, 50%, and 90% values of the pulse on both the **leading and trailing edges.**

| Leading edge: | 10%: | $2 \mu s$ | Trailing edge: | 90%: | 20 μs |

|---------------|------|-----------|----------------|------|-------|

|               | 50%: | 5 μs      |                | 50%: | 25 μs |

|               | 90%: | 8 µs      |                | 10%: | 30 µs |

Pulse width: 50% of leading edge to 50% of trailing edge.

$$t_w = 25 \ \mu s - 5 \ \mu s = 20 \ \mu s$$

Rise time: 10% of rising edge to 90% of rising edge.

$$t_r = 8 \, \mu s - 2 \, \mu s = 6 \, \mu s$$

Fall time: 90% of falling edge to 10% of falling edge.

$$t_f = 30 \ \mu s - 20 \ \mu s = 10 \ \mu s$$

#### **III** SECTION 1.5 REVIEW PROBLEMS

A digital circuit produces a waveform that can be described by the following periodic bit pattern: 0011001100110011.

- 1.12 What is the duty cycle of the waveform?

- 1.13 Write the bit pattern of a waveform with the same duty cycle and twice the frequency of the original.

- 1.14 Write the bit pattern of a waveform having the same frequency as the original and a duty cycle of 75%.

#### SUMMARY

- The two basic areas of electronics are analog and digital electronics. Analog electronics deals with continuously variable quantities; digital electronics represents the world in discrete steps.

- 2. Digital logic uses defined voltage levels, called logic levels, to represent binary numbers within an electronic system.

- 3. The higher voltage in a digital system represents the binary digit 1 and is called a logic HIGH or logic 1. The lower voltage in a system represents the binary digit 0 and is called a logic LOW or logic 0.

- 4. The logic levels of multiple locations in a digital circuit can be combined to represent a multibit binary number.

- 5. Binary is a positional number system (base 2) with two digits, 0 and 1, and positional multipliers that are powers of 2.

- 6. The bit with the largest positional weight in a binary number is called the most significant bit (MSB); the bit with the smallest positional weight is called the least significant bit (LSB). The MSB is also the leftmost bit in the number; the LSB is the rightmost bit.

7. A decimal number can be converted to binary by sum of powers of 2 (add place values to get a total) or repeated division by 2 (divide by 2 until quotient is 0; remainders are the binary value).

- 8. The hexadecimal number system is based on 16. It uses 16 digits, from 0–9 and A–F, with power-of-16 multipliers.

- Each hexadecimal digit uniquely corresponds to a 4-bit binary value. Hex digits can thus be used as shorthand for binary.

- A digital waveform is a sequence of bits over time. A waveform can be periodic (repetitive), aperiodic (nonrepetitive), or pulsed (a single variation and return between logic levels.)

- 11. Periodic waveforms are measured by period (T: time for one cycle), time HIGH ( $t_h$ ), time LOW ( $t_l$ ), frequency (f: number of cycles per second), and duty cycle (DC or %DC: fraction of cycle in HIGH state).

- 12. Pulse waveforms are measured by pulse width  $(t_w)$ : time from 50% of leading edge of 50% of trailing edge), rise time  $(t_r)$ : time from 10% to 90% of rising edge) and fall time  $(t_f)$ : time from 90% to 10% of falling edge).

#### GLOSSARY

**Amplitude** The instantaneous voltage of a waveform. Often used to mean maximum amplitude, or peak voltage, of a pulse.

**Analog** A way of representing some physical quantity, such as temperature or velocity, by a proportional continuous voltage or current. An analog voltage or current can have any value within a defined range.

**Aperiodic waveform** A time-varying sequence of logic HIGHs and LOWs that does not repeat.

**Binary number system** A number system used extensively in digital systems, based on the number 2. It uses two digits to write any number.

**Bit** Binary digit. A 0 or a 1.

**Continuous** Smoothly connected. An unbroken series of consecutive values with no instantaneous changes.

**Digital** A way of representing a physical quantity by a series of binary numbers. A digital representation can have only specific discrete values.

**Digital waveform** A series of logic 1s and 0s plotted as a function of time.

**Discrete** Separated into distinct segments or pieces. A series of discontinuous values.

**Duty cycle (DC)** Fraction of the total period that a digital waveform is in the HIGH state.  $DC = t_h/T$  (often expressed as a percentage:  $\%DC = t_h/T \times 100\%$ ).

**Edge** The part of the pulse that represents the transition from one logic level to the other.

**Fall time** ( $t_f$ ) Elapsed time from the 90% point to the 10% point of the falling edge of a pulse.

**Falling edge** The part of a pulse where the logic level is in transition from a HIGH to a LOW.

**Frequency** (f) Number of times per second that a periodic waveform repeats. f = 1/T Unit: Hertz (Hz).

**Hexadecimal number system** Base-16 number system. Hexadecimal numbers are written with sixteen digits, 0–9 and A–F, with power-of-16 positional multipliers.

**Leading edge** The edge of a pulse that occurs earliest in time.

**Least significant bit (LSB)** The rightmost bit of a binary number. This bit has the number's smallest positional multiplier.

**Logic HIGH** The higher of two voltages in a digital system with two logic levels.

**Logic level** A voltage level that represents a defined digital state in an electronic circuit.

**Logic LOW** The lower of two voltages in a digital system with two logic levels.

**Most significant bit (MSB)** The leftmost bit in a binary number. This bit has the number's largest positional multiplier.

**Negative logic** A system in which logic LOW represents binary digit 1 and logic HIGH represents binary digit 0.

**Period** (*T*) Time required for a period waveform to repeat. Unit: seconds (s).

**Periodic waveform** A time-varying sequence of logic HIGHs and LOWs that repeats over a specified period of time.

**Positional notation** A system of writing numbers in which the value of a digit depends not only on the digit, but also on its placement within a number.

**Positive logic** A system in which logic LOW represents binary digit 0 and logic HIGH represents binary digit 1.

**Pulse** A momentary variation of voltage from one logic level to the opposite level and back again.

**Pulse width**  $(t_w)$  Elapsed time from the 50% point of the leading edge of a pulse to the 50% point of the trailing edge.

**Radix point** The generalized form of a decimal point. In any positional number system, the radix point marks the dividing line between positional multipliers that are positive and negative powers of the system's number base.

**Rise time**  $(t_r)$  Elapsed time from the 10% point to the 90% point of the rising edge of a pulse.

**Rising edge** The part of a pulse where the logic level is in transition from a LOW to a HIGH.

**Time HIGH**  $(t_h)$  Time during one period that a waveform is in the HIGH state. Unit: seconds (s).

**Time LOW**  $(t_l)$  Time during one period that a waveform is in the LOW state. Unit: seconds (s).

**Trailing edge** The edge of a pulse that occurs latest in time.

#### PROBLEMS

Problem numbers set in color indicate more difficult problems: those with underlines indicate most difficult problems.

#### Section 1.1 Digital Versus Analog Electronics

- **1.1** Which of the following quantities is analog in nature and which digital? Explain your answers.

- a. Water temperature at the beach

- b. Weight of a bucket of sand

- c. Grains of sand in a bucket

- d. Waves hitting the beach in one hour

- e. Height of a wave

- f. People in a square mile

#### Section 1.2 Digital Logic Levels

**1.2** A digital logic system is defined by the voltages 3.3 volts and 0 volts. For a positive logic system, state which voltage corresponds to a logic 0 and which to a logic 1.

#### Section 1.3 The Binary Number System

**1.3** Calculate the decimal values of each of the following binary numbers:

a. 100

b. 1000

c. 11001

d. 110

d. 110

j. 10111001

- 1.4 Translate each of the following combinations of HIGH(H) and LOW (L) logic levels to binary numbers using positive logic:

- a. HHLH

d. LLLH

b. LHLH

e. HLLL

- c. HLHL

- **1.5** List the sequence of binary numbers from 101 to 1000.

- **1.6** List the sequence of binary numbers from 10000 to 11111.

- 1.7 What is the decimal value of the most significant bit for the numbers in Problem 1.6

- **1.8** Convert the following decimal numbers to binary. Use the sum-of-powers-of-2 method for parts a, c, e, and g. Use the repeated-division-by-2 method for parts b, d, f, and h.

- **a.** 75<sub>10</sub>

- **e.** 63<sub>10</sub>

- **b.** 83<sub>10</sub>

- **f.** 64<sub>10</sub>

- **c.** 237<sub>10</sub>

- **g.** 4087<sub>10</sub>

- **d.** 198<sub>10</sub>

- **h.** 8193<sub>10</sub>

- **1.9** Convert the following fractional binary numbers to their decimal equivalents.

- **a.** 0.101

- **b.** 0.011

- **c.** 0.1101

- **1.10** Convert the following fractional binary numbers to their decimal equivalents.

- **a.** 0.01

- **c.** 0.010101

- **b.** 0.0101

- **d.** 0.01010101

- 1.11 The numbers in Problem 1.10 are converging to a closer and closer binary approximation of a simple fraction that can be expressed by decimal integers a/b. What is the fraction?

- **1.12** What is the simple decimal fraction (*a/b*) represented by the repeating binary number 0.101010 . . . ?

- **1.13** Convert the following decimal numbers to their binary equivalents. If a number has an integer part larger than 0, calculate the integer and fractional parts separately.

- **a.** 0.75<sub>10</sub>

- **e.** 1.75<sub>10</sub>

- **b.** 0.625<sub>10</sub>

- **f.** 3.95<sub>10</sub>

- **c.** 0.1875<sub>10</sub>

- **g.** 67.84<sub>10</sub>

- **d.** 0.65<sub>10</sub>

#### Section 1.4 Hexadecimal Numbers

- **1.14** Write all the hexadecimal numbers in sequence from 308H to 321H inclusive.

- **1.15** Write all the hexadecimal numbers in sequence from 9F7H to A03H inclusive.

- **1.16** Convert the following hexadecimal numbers to their decimal equivalents.

- **a.** 1A0H

- e. F3C8H

- **b.** 10AH

- **f.** D3B4H

- c. FFFH

- **g.** C000H

- **d.** 1000H

- **h.** 30BAFH

- 1.17 Convert the following decimal numbers to their hexadeci-

- mal equivalents.

- **a.** 709<sub>10</sub>

- **b.** 1889<sub>10</sub>

- **c.** 4095<sub>10</sub>

- **d.** 4096<sub>10</sub>

- **e.** 10128<sub>10</sub>

- **f.** 32000<sub>10</sub>

- **g.** 32768<sub>10</sub>

- 1.18 Convert the following hexadecimal numbers to their bi

- **a.** F3C8H

nary equivalents.

- **b.** D3B4H

- **c.** 8037H

- d. FABDH

- e. 30ACH

- **f.** 3E7B6H

- g. 743DCFH

- **1.19** Convert the following binary numbers to their hexadecimal equivalents.

- **a.** 1011111010000110<sub>2</sub>

- **b.**  $101101101010_2$

- **c.** 110001011011<sub>2</sub>

- **d.** 1101011111000100<sub>2</sub>

- **e.** 101010111110000101<sub>2</sub>

- **f.** 11001100010110111<sub>2</sub>

#### Section 1.5 Digital Waveforms

- 1.20 Calculate the time LOW, time HIGH, period, frequency, and percent duty cycle for the waveforms shown in Figure 1.12. How are the waveforms similar? How do they differ?

- **1.21** Which of the waveforms in Figure 1.13 are periodic and which are aperiodic? Explain your answers.

- **1.22** Sketch the pulse waveforms represented by the following strings of 0s and 1s. State which waveforms are periodic and which are aperiodic.

- a. 11001111001110110000000110110101

- **b.** 111000111000111000111000111

- c. 11111111100000000111111111111111111

- **d.** 0110011001100110011001100110

- e. 011101101001101001011010011101110

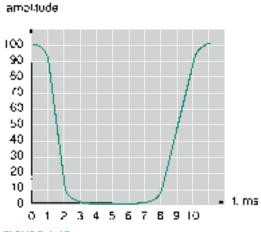

- **1.23** Calculate the pulse width, rise time, and fall time of the pulse shown in Figure 1.14.

- **1.24** Repeat Problem 1.23 for the pulse shown in Figure 1.15.

FIGURE 1.12 Problem 1.20: Periodic Waveforms

FIGURE 1.13 Problem 1.21: Aperiodic and Periodic Waveforms

% of full

FIGURE 1.14 Problem 1.23: Pulse

FIGURE 1.15 Problem 1.24: Pulse

#### ANSWERS TO SECTION REVIEW PROBLEMS

#### Section 1.1

**1.1** An analog audio system makes a direct copy of the recorded sound waves. A digital system stores the sound as a series of binary numbers.

#### Section 1.3

**1.2** 64; **1.3.** 128; **1.4.** 1010000, 1010001, 1010010, 1010011, 1010100, 1010101, 1010110, 1010111; **1.5.** 80, 81, 82, 83, 84, 85, 86, 87.

#### Section 1.4a

**1.6** FA9, FAA, FAB, FAC, FAD, FAE, FAF, FB0, **1.7** 1F9, 1FA, 1FB, 1FC, 1FD, 1FE, 1FF, 200.

#### Section 1.4b

**1.8** 41743<sub>10</sub>.

Section 1.4c

**1.9** 1FC9.

#### Section 1.4d

**1.10** 1001001101001011. **1.11** C8349.

#### Section 1.5

**1.12** 50%; **1.13** 0101010101010101; **1.14** 0111011101111.

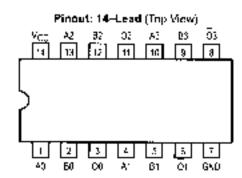

## Logic Functions and Gates

#### OUTLINE

- **2.1** Basic Logic Functions

- 2.2 Logic Switches and LED Indicators

- 2.3 Derived Logic Functions

- 2.4 DeMorgan's Theorems and Gate Equivalence

- 2.5 Enable and Inhibit Properties of Logic Gates

- 2.6 Integrated Circuit Logic Gates

#### CHAPTER OBJECTIVES

Upon successful completion of this chapter, you will be able to:

- Describe the basic logic functions: AND, OR, and NOT

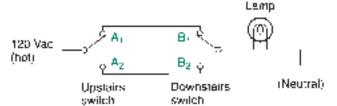

- Draw simple switch circuits to represent AND, OR and Exclusive OR functions.

- Draw simple logic switch circuits for single-pole single-throw (SPST) and normally open and normally closed pushbutton switches.

- Describe the use of light-emitting diodes (LEDs) as indicators of logic HIGH and LOW states.

- Describe those logic functions derived from the basic ones: NAND, NOR, Exclusive OR, and Exclusive NOR.

- Explain the concept of active levels and identify active LOW and HIGH terminals of logic gates.

- Choose appropriate logic functions to solve simple design problems.

- · Draw the truth table of any logic gate.

- Draw any logic gate, given its truth table.

- Draw the DeMorgan equivalent form of any logic gate.

- Determine when a logic gate will pass a digital waveform and when it will block the signal.

- Describe several types of integrated circuit packaging for digital logic gates.

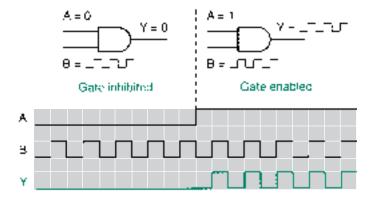

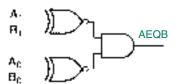

A ll digital logic functions can be synthesized by various combinations of the three basic logic functions: AND, OR, and NOT. These so-called Boolean functions are the basis for all further study of combinational logic circuitry. (Combinational logic circuits are digital circuits whose outputs are functions of their inputs, regardless of the order the inputs are applied.) Standard circuits, called logic gates, have been developed for these and for more complex digital logic functions.

Logic gates can be represented in various forms. A standard set of distinctive-shape symbols has evolved as a universally understandable means of representing the various functions in a circuit. A useful pair of mathematical theorems, called DeMorgan's theorems, enables us to draw these gate symbols in different ways to represent different aspects of the same function. A newer way of representing standard logic gates is outlined in IEEE/ANSI Standard 91-1984, a standard copublished by the Institute of Electrical and

Electronic Engineers and the American National Standards Institute. It uses a set of symbols called rectangular-outline symbols.

Logic gates can be used as electronic switches to block or allow passage of digital waveforms. Each logic gate has a different set of properties for enabling (passing) or inhibiting (blocking) digital waveforms.

## 2.1 Basic Logic Functions

#### KEY TERMS

**Boolean variable** A variable having only two possible values, such as HIGH/LOW, 1/0, On/Off, or True/False.

**Boolean algebra** A system of algebra that operates on Boolean variables. The binary (two-state) nature of Boolean algebra makes it useful for analysis, simplification, and design of combinational logic circuits.

**Boolean expression** An algebraic expression made up of Boolean variables and operators, such as AND, OR, or NOT. Also referred to as a **Boolean function** or a **logic function**.

**Logic gate** An electronic circuit that performs a Boolean algebraic function.

At its simplest level, a digital circuit works by accepting logic 1s and 0s at one or more inputs and producing 1s or 0s at one or more outputs. A branch of mathematics known as **Boolean algebra** (named after 19th-century mathematician George Boole) describes the relation between inputs and outputs of a digital circuit. We call these input and output values **Boolean variables** and the functions **Boolean expressions**, **logic functions**, or **Boolean functions**. The distinguishing characteristic of these functions is that they are made up of variables and constants that can have only two possible values: 0 or 1.

All possible operations in Boolean algebra can be created from three basic logic functions: AND, OR, and NOT.<sup>1</sup> Electronic circuits that perform these logic functions are called **logic gates.** When we are analyzing or designing a digital circuit, we usually don't concern ourselves with the actual circuitry of the logic gates, but treat them as black boxes that perform specified logic functions. We can think of each variable in a logic function as a circuit input and the whole function as a circuit output.

In addition to gates for the three basic functions, there are also gates for compound functions that are derived from the basic ones. NAND gates combine the NOT and AND functions in a single circuit. Similarly, NOR gates combine the NOT and OR functions. Gates for more complex functions, such as Exclusive OR and Exclusive NOR, also exist. We will examine all these devices later in the chapter.

#### NOT, AND, and OR Functions

#### KEY TERMS

**Truth table** A list of all possible input values to a digital circuit, listed in ascending binary order, and the output response for each input combination.

**Inverter** Also called a NOT gate or an inverting buffer. A logic gate that changes its input logic level to the opposite state.

**Bubble** A small circle indicating logical inversion on a circuit symbol.

<sup>&</sup>lt;sup>1</sup>Words in uppercase letters represent either logic functions (AND, OR, NOT) or logic levels (HIGH, LOW). The same words in lowercase letters represent their conventional nontechnical meanings.

**Distinctive-shape symbols** Graphic symbols for logic circuits that show the function of each type of gate by a special shape.

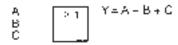

**IEEE/ANSI Standard 91-1984** A standard format for drawing logic circuit symbols as rectangles with logic functions shown by a standard notation inside the rectangle for each device.

**Rectangular-outline symbols** Rectangular logic gate symbols that conform to IEEE/ANSI Standard 91-1984.

**Qualifying symbol** A symbol in IEEE/ANSI logic circuit notation, placed in the top center of a rectangular symbol, that shows the function of a logic gate. Some of the qualifying symbols include: 1 = "buffer"; & = "AND";  $\geq 1 = \text{"OR"}$

**Buffer** An amplifier that acts as a logic circuit. Its output can be inverting or non-inverting.

**Table 2.1** NOT Function Truth Table

| A | Y   |

|---|-----|

| 0 | 1 0 |

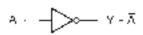

a. Distinctive-shape

b Rectangular-outline (ICEC std. 91-1964)

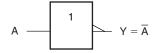

FIGURE 2.1

Inverter Symbols

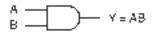

**Table 2.2** 2-input AND Function Truth Table

| A | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

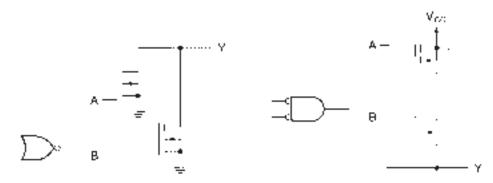

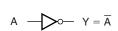

#### **NOT Function**

The NOT function, the simplest logic function, has one input and one output. The input can be either HIGH or LOW (1 or 0), and the output is always the opposite logic level. We can show these values in a **truth table**, a list of all possible input values and the output resulting from each one. Table 2.1 shows a truth table for a NOT function, where A is the input variable and Y is the output.

The NOT function is represented algebraically by the Boolean expression:

$$Y = \overline{A}$$

This is pronounced "Y equals NOT A" or "Y equals A bar." We can also say "Y is the complement of A."

The circuit that produces the NOT function is called the NOT gate or, more usually, the **inverter.** Several possible symbols for the inverter, all performing the same logic function, are shown in Figure 2.1.

The symbols shown in Figure 2.1a are the standard **distinctive-shape symbols** for the inverter. The triangle represents an amplifier circuit, and the **bubble** (the small circle on the input or output) represents inversion. There are two symbols because sometimes it is convenient to show the inversion at the input and sometimes it is convenient to show it at the output.

Figure 2.1b shows the **rectangular-outline** inverter symbol specified by **IEEE/ANSI Standard 91-1984.** This standard is most useful for specifying the symbols for more complex digital devices. We will show the basic gates in both distinctive-shape and rectangular-outline symbols, although most examples will use the distinctive-shape symbols.

The "1" in the top center of the IEEE symbol is a **qualifying symbol**, indicating the logic gate function. In this case, it shows that the circuit is a **buffer**, an amplifying circuit used as a digital logic element. The arrows at the input and output of the two IEEE symbols show inversion, like the bubbles in the distinctive-shape symbols.

#### **AND Function**

#### KEY TERMS

**AND gate** A logic circuit whose output is HIGH when all inputs (e.g., *A* AND *B* AND *C*) are HIGH.

**Logical product** AND function.

The AND function combines two or more input variables so that the output is HIGH only if *all* the inputs are HIGH. The truth table for a 2-input AND function is shown in Table 2.2.

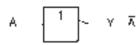

a. Distinctive-shape

b. Rectangular-outline

#### FIGURE 2.2

2-Input AND Gate Symbols

Algebraically, this is written:

$$Y = A \cdot B$$

Pronounce this expression "Y equals A AND B." The AND function is similar to multiplication in linear algebra and thus is sometimes called the **logical product.** The dot between variables may or may not be written, so it is equally correct to write Y = AB. The logic circuit symbol for an **AND gate** is shown in Figure 2.2 in both distinctive-shape and IEEE/ANSI rectangular-outline form. The qualifying symbol in IEEE/ANSI notation is the ampersand (&).

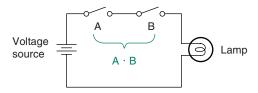

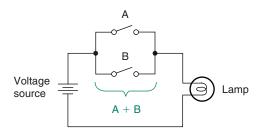

We can also represent the AND function as a set of switches in series, as shown in Figure 2.3. The circuit consists of a voltage source, a lamp, and two series switches. The lamp turns on when switches *A* AND *B* are both closed. For any other condition of the switches, the lamp is off.

FIGURE 2.3

AND Function Represented by Switches

**Table 2.3** 3-input AND Function Truth Table

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Table 2.3 shows the truth table for a 3-input AND function. Each of the three inputs can have two different values, which means the inputs can be combined in  $2^3 = 8$  different ways. In general, n binary (i.e., two-valued) variables can be combined in  $2^n$  ways.

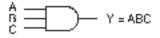

Figure 2.4 shows the logic symbols for the device. The output is HIGH only when all inputs are HIGH.

#### FIGURE 2.4

3-Input AND Gate Symbols

a. Distinctive shape

b. Rectangular-outline

## Table 2.4 2-input OR

Function Truth Table

# A B Y 0 0 0 0 1 1 1 0 1 1 1 1

#### **OR Function**

#### KEY TERMS

**OR gate** A logic circuit whose output is HIGH when at least one input (e.g., *A* OR *B* OR *C*) is HIGH.

**Logical sum** OR function.

The OR function combines two or more input variables in such a way as to make the output variable HIGH if *at least one* input is HIGH. Table 2.4 gives the truth table for the 2-input OR function.

Distinctive-shape

b. Rectangular-outline

#### FIGURE 2.5

2-Input OR Gate Symbols

The algebraic expression for the OR function is:

$$Y = A + B$$

which is pronounced "Y equals A OR B." This is similar to the arithmetic addition function, but it is not the same. The last line of the truth table tells us that 1 + 1 = 1 (pronounced "1 OR 1 equals 1"), which is not what we would expect in standard arithmetic. The similarity to the addition function leads to the name **logical sum.** (This is different from the "arithmetic sum," where, of course, 1 + 1 does not equal 1.)

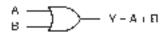

Figure 2.5 shows the logic circuit symbols for an **OR gate.** The qualifying symbol for the OR function in IEEE/ANSI notation is "≥1," which tells us that *one or more* inputs must be HIGH to make the output HIGH.

The OR function can be represented by a set of switches connected in parallel, as in Figure 2.6. The lamp is on when either switch A OR switch B is closed. (Note that the lamp is also on if both A and B are closed. This property distinguishes the OR function from the Exclusive OR function, which we will study later in this chapter.)

#### FIGURE 2.6

OR Function Represented by Switches

**Table 2.5** 3-input OR Function Truth Table

| $\boldsymbol{A}$ | В | C | Y |  |

|------------------|---|---|---|--|

| 0                | 0 | 0 | 0 |  |

| 0                | 0 | 1 | 1 |  |

| 0                | 1 | 0 | 1 |  |

| 0                | 1 | 1 | 1 |  |

| 1                | 0 | 0 | 1 |  |

| 1                | 0 | 1 | 1 |  |

| 1                | 1 | 0 | 1 |  |

| 1                | 1 | 1 | 1 |  |

|                  |   |   |   |  |

Like AND gates, OR gates can have several inputs, such as the 3-input OR gates shown in Figure 2.7. Table 2.5 shows the truth table for this gate. Again, three inputs can be combined in eight different ways. The output is HIGH when at least one input is HIGH.

#### FIGURE 2.7

3-Input OR Gate Symbols

a. Distinctive-shape

b. Aectangular-outline

#### **III** EXAMPLE 2.1

#### **Application**

State which logic function is most suitable for the following operations. Draw a set of switches to represent each function.

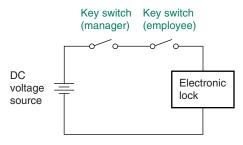

- 1. A manager and one other employee both need a key to open a safe.

- 2. A light comes on in a storeroom when either (or both) of two doors is open. (Assume the switch closes when the door opens.)

- 3. For safety, a punch press requires two-handed operation.

#### **SOLUTION**

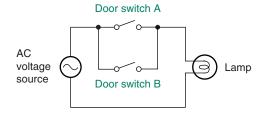

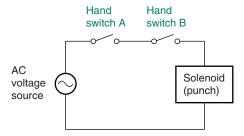

1. Both keys are required, so this is an AND function. Figure 2.8a shows a switch representation of the function.

- 2. One or more switches closed will turn on the lamp. This OR function is shown in Figure 2.8b.

- 3. Two switches are required to activate a punch press, as shown in Figure 2.8c. This is an AND function.

#### FIGURE 2.8

Example 2.1

a. Two keys to open a safe (AND)

b. One or more switches turn on a lamp (OR)

c. Two switches are required to activate a punch press (AND)

#### **Active Levels**

#### KEY TERMS

**Active level** A logic level defined as the "ON" state for a particular circuit input or output. The active level can be either HIGH or LOW.

**Active HIGH** An active-HIGH terminal is considered "ON" when it is in the logic HIGH state. Indicated by the absence of a bubble at the terminal in distinctive-shape symbols.

**Active LOW** An active-LOW terminal is considered "ON" when it is in the logic LOW state. Indicated by a bubble at the terminal in distinctive-shape symbols.

An **active level** of a gate input or output is the logic level, either HIGH or LOW, of the terminal when it is performing its designated function. An **active LOW** is shown by a bubble or an arrow symbol on the affected terminal. If there is no bubble or arrow, we assume the terminal is **active HIGH.**

The AND function has active-HIGH inputs and an active-HIGH output. To make the output HIGH, inputs A AND B must both be HIGH. The gate performs its designated function only when all inputs are HIGH.

The OR gate requires input *A* OR input *B* to be HIGH for its output to be HIGH. The HIGH active levels are shown by the absence of bubbles or arrows on the terminals.

#### **■ SECTION REVIEW PROBLEM FOR SECTION 2.1**

A 4-input gate has input variables A, B, C, and D and output Y. Write a descriptive sentence for the active output state(s) if the gate is

2.1 AND;

2.2 OR.

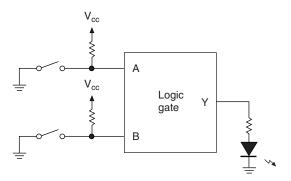

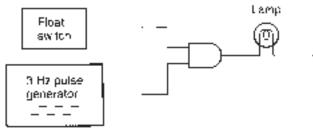

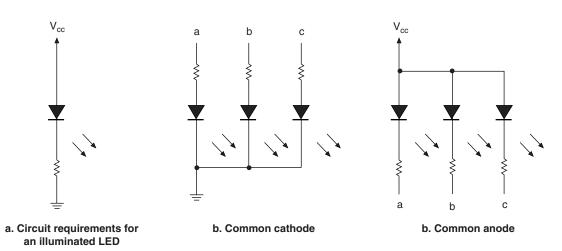

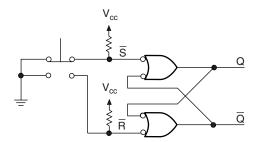

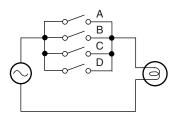

## 2.2 Logic Switches and LED Indicators

Before continuing on, we should examine a few simple circuits that can be used for input or output in a digital circuit. Single-pole single-throw (SPST) and pushbutton switches can be used, in combination with resistors, to generate logic voltages for circuit inputs. Light emitting diodes (LEDs) can be used to monitor outputs of circuits.

#### **Logic Switches**

#### KEY TERMS

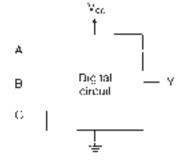

$V_{\rm CC}$  The power supply voltage in a transistor-based electronic circuit. The term often refers to the power supply of digital circuits.

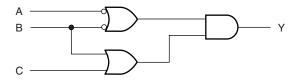

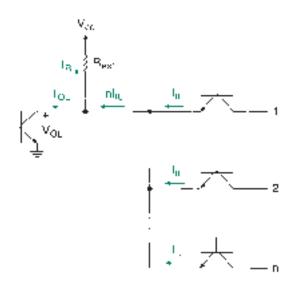

**Pull-up resistor** A resistor connected from a point in an electronic circuit to the power supply of that circuit.

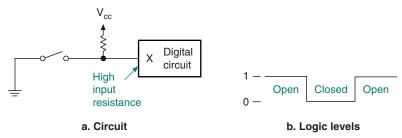

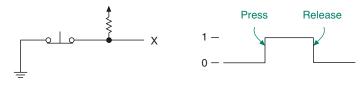

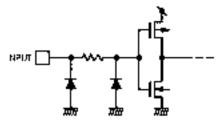

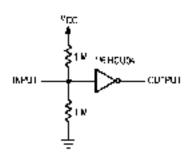

Figure 2.9a shows a single-pole single-throw (SPST) switch connected as a logic switch. An important premise of this circuit is that the input of the digital circuit to which it is connected has a very high resistance to current. When the switch is open, the current flowing through the **pull-up resistor** from  $V_{\rm CC}$  to the digital circuit is very small. Since the current is small, Ohm's law states that very little voltage drops across the pull-up resistor; the voltage is about the same at one end as at the other. Therefore, an open switch generates a logic HIGH at point X.

FIGURE 2.9 SPST Logic Switch

When the switch is closed, the majority of current flows to ground, limited only by the value of the pull-up resistor. (Since a pull-up resistor is typically between 1 k $\Omega$  and 10 k $\Omega$ , the LOW-state current in the resistor is about 0.5 mA to 5 mA.) Point X is approximately at ground potential, or logic LOW. Thus the switch generates a HIGH when open and a LOW when closed. The pull-up resistor provides a connection to  $V_{\rm CC}$  in the HIGH state

and limits power supply current in the LOW state. Figure 2.9b shows the voltage levels when the switch is closed and when it is open.

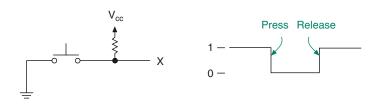

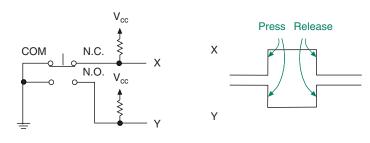

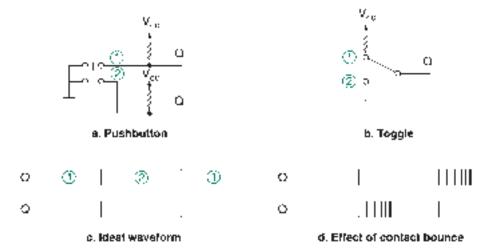

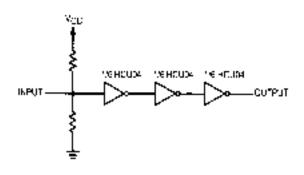

Figure 2.10 shows how pushbuttons can be used as logic inputs. Figure 2.10a shows a normally open pushbutton and a pull-up resistor. The pushbutton has a spring-loaded plunger that makes a connection between two internal contacts when pressed. When released, the spring returns the plunger to the "normal" (open) state. The logic voltage at X is normally HIGH, but LOW when the button is pressed.

#### a. Normally open pushbutton

#### b. Normally closed pushbutton

c. Two-pole pushbutton

#### FIGURE 2.10

Pushbuttons as Logic Switches

Figure 2.10b shows a normally closed pushbutton. The internal spring holds the plunger so that the connection is normally made between the two contacts. When the button is pressed, the connection is broken and the resistor pulls up the voltage at X to a logic HIGH. At rest, X is grounded and the voltage at X is LOW.

It is sometimes desirable to have normally HIGH and normally LOW levels available from the same switch. The two-pole pushbutton in Figure 2.10c provides such a function. The switch has a normally open and a normally closed contact. One contact of each switch is connected to the other, in an internal COMMON connection, allowing the switch to have three terminals rather than four. The circuit has two pull-up resistors, one for X and one for Y. X is normally HIGH and goes LOW when the switch is pressed. Y is opposite.

#### **LED Indicators**

#### KEY TERMS

**LED** Light-emitting diode. An electronic device that conducts current in one direction only and illuminates when it is conducting.

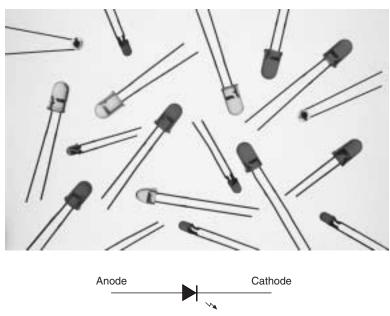

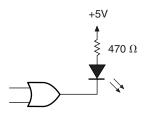

A device used to indicate the status of a digital output is the **light-emitting diode** or **LED.** This is sometimes pronounced as a word ("led") and sometimes said as separate initials ("ell ee dee"). This device comes in a variety of shapes, sizes, and colors, some of which are shown in the photo of Figure 2.11. The circuit symbol, shown in Figure 2.12, has two terminals, called the anode (positive) and cathode (negative). The arrow coming from the symbol indicates emitted light.

FIGURE 2.11 LEDs

FIGURE 2.12 Light-Emitting Diode (LED)

Condition for LED Illumination

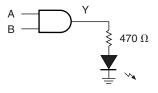

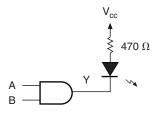

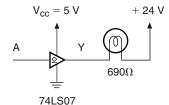

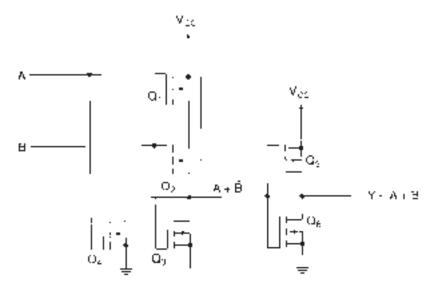

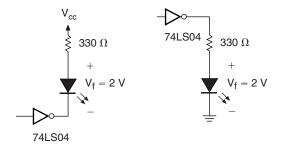

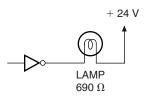

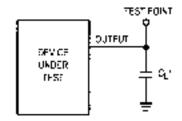

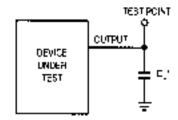

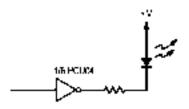

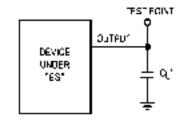

FIGURE 2.14 AND Gate Driving an LED The electrical requirements for the LED are simple: current flows through the LED if the anode is more positive than the cathode by more than a specified value (about 1.5 volts). If enough current flows, the LED illuminates. If more current flows, the illumination is brighter. (If too much flows, the LED burns out, so a series resistor is used to keep the current in the required range.) Figure 2.13 shows a circuit in which an LED illuminates when a switch is closed.

Figure 2.14 shows an AND gate driving an LED. In Figure 2.14a, the LED is on when *Y* is HIGH (5 volts), since the anode of the LED is more positive than the cathode.

a. LED on when Y is HIGH

b. LED on when Y is LOW

**FIGURE 2.15**

LED Indicates Status of Switch

In Figure 2.14b, the LED turns on when Y is LOW (0 volts), again since the anode is more positive than the cathode.

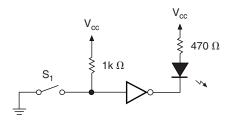

Figure 2.15 shows a circuit in which an LED indicates the status of a logic switch. When the switch is open, the  $1~\mathrm{k}\Omega$  pull-up applies a HIGH to the inverter input. The inverter output is LOW, turning on the LED (anode is more positive than cathode). When the switch is closed, the inverter input is LOW. The inverter output is HIGH (same value as  $V_{\rm CC}$ ), making anode and cathode voltages equal. No current flows through the LED, and it is therefore off. Thus, the LED is on for a HIGH state at the switch and off for a LOW. Note, however, that the LED is *on* when the inverter output is *LOW*.

#### **■ SECTION 2.2 REVIEW PROBLEM**

2.3 A single-pole single-throw switch is connected such that one end is grounded and one end is connected to a 1 k $\Omega$  pull-up resistor. The other end of the resistor connects to the circuit power supply,  $V_{\rm CC}$ . What logic level does the switch provide when it is open? When it is closed?

## 2.3 Derived Logic Functions

#### KEY TERMS

**NAND gate** A logic circuit whose output is LOW when all inputs are HIGH.

**NOR gate** A logic circuit whose output is LOW when at least one input is HIGH.

**Exclusive OR gate** A 2-input logic circuit whose output is HIGH when one input (but not both) is HIGH.

**Exclusive NOR gate** A 2-input logic circuit whose output is the complement of an Exclusive OR gate.

**Coincidence gate** An Exclusive NOR gate.

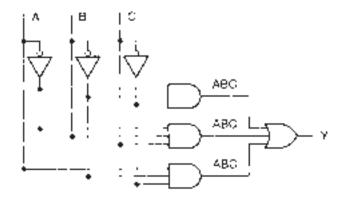

The basic logic functions, AND, OR, and NOT, can be combined to make any other logic function. Special logic gates exist for several of the most common of these derived functions. In fact, for reasons we will discover later, two of these derived-function gates, NAND and NOR, are the most common of all gates, and *each* can be used to create any logic function.

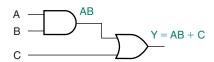

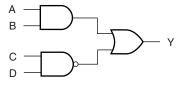

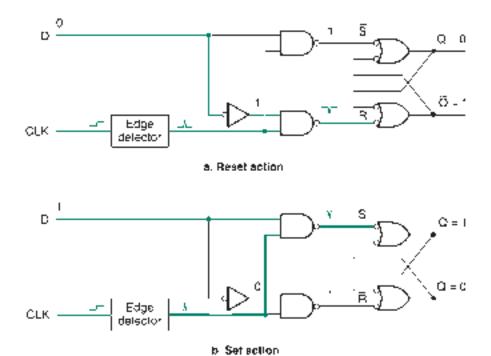

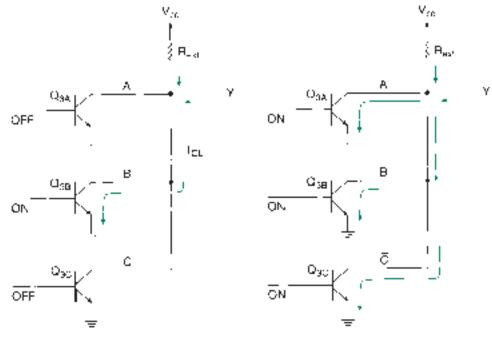

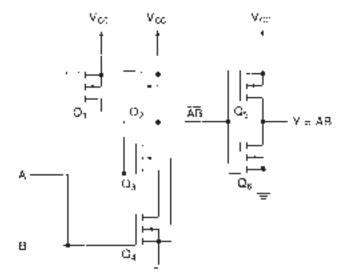

#### NAND and NOR Functions

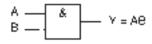

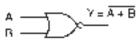

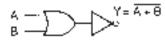

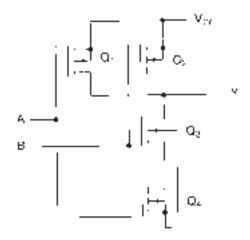

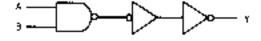

The names NAND and NOR are contractions of NOT AND and NOT OR, respectively. The NAND is generated by inverting the output of an AND function. The symbols for the **NAND gate** and its equivalent circuit are shown in Figure 2.16.

The algebraic expression for the NAND function is:

$$Y = \overline{A \cdot B}$$

#### FIGURE 2.16 NAND Gate Symbols

**Table 2.6** NAND Function Truth Table

| A | В | Y |  |

|---|---|---|--|

| 0 | 0 | 1 |  |

| 0 | 1 | 1 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | 0 |  |

**Table 2.7** NOR Function Truth Table

| A | В | Y           |  |

|---|---|-------------|--|

| 0 | 0 | 1           |  |

| 0 | 1 | 0           |  |

| 1 | 0 | 0<br>0<br>0 |  |

| 1 | 1 | 0           |  |

The entire function is inverted because the bubble is on the NAND gate output.

Table 2.6 shows the NAND gate truth table. The output is LOW when A AND B are HIGH.

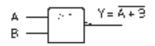

We can generate the NOR function by inverting the output of an OR gate. The NOR function truth table is shown in Table 2.7. The truth table tells us that the output is LOW when *A* OR *B* is HIGH.

Figure 2.17 shows the logic symbols for the **NOR gate.**

a. Distinctive-shape

b. Réctangular-outline

c. Equivalent circult

FIGURE 2.17

NOR Gate Symbols

The algebraic expression for the NOR function is:

$$Y = \overline{A + B}$$

The entire function is inverted because the bubble is on the gate output.

We know that the outputs of both gates are active LOW because of the bubbles on the output terminals. The inputs are active HIGH because there are no bubbles on the input terminals.

#### **Multiple-Input NAND and NOR Gates**

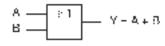

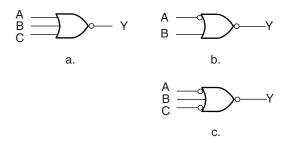

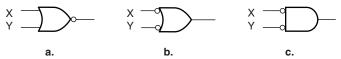

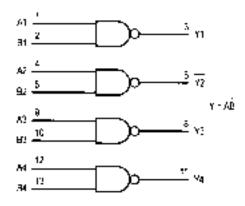

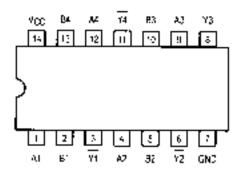

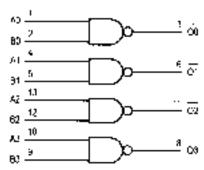

Table 2.8 shows the truth tables of the 3-input NAND and NOR functions. The logic circuit symbols for these gates are shown in Figure 2.18.

Table 2.8

3-input NAND and NOR Function Truth Tables

| A | В | С | $\overline{A \cdot B \cdot C}$ | $\overline{A+B+C}$ |

|---|---|---|--------------------------------|--------------------|

| 0 | 0 | 0 | 1                              | 1                  |

| 0 | 0 | 1 | 1                              | 0                  |

| 0 | 1 | 0 | 1                              | 0                  |

| 0 | 1 | 1 | 1                              | 0                  |

| 1 | 0 | 0 | 1                              | 0                  |

| 1 | 0 | 1 | 1                              | 0                  |

| 1 | 1 | 0 | 1                              | 0                  |

| 1 | 1 | 1 | 0                              | 0                  |

The truth tables of these gates can be generated by understanding the active levels of the gate inputs and outputs. The NAND output is LOW when A AND B AND C are HIGH. This is shown in the last line of the NAND truth table. The NOR output is LOW if one or more of A OR B OR C is HIGH. This describes all lines of the NOR truth table except the first.

# **FIGURE 2.18**

3-Input NAND and NOR Gates

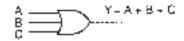

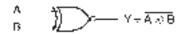

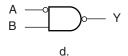

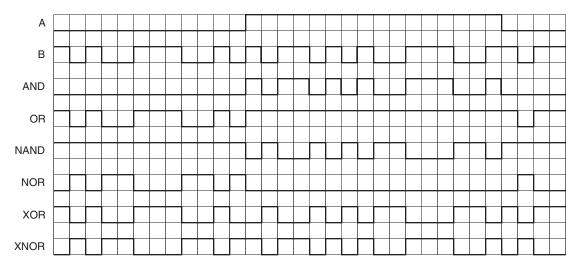

# **Exclusive OR and Exclusive NOR Functions**